Содержание

В многозадачной системе, использующей многозадачность , вы должны запоминать сразу несколько процессов . Если доступны инструменты виртуализации памяти, каждый процесс может создать собственное виртуальное адресное пространство, начиная с нулевого адреса. Затем каждый процесс (или его машинные инструкции ) будет работать с логическими адресами, которые автоматически преобразуются MMU в физические адреса при доступе к ОЗУ. Сегодня MMU обычно размещается в процессоре, но также может быть независимой схемой.

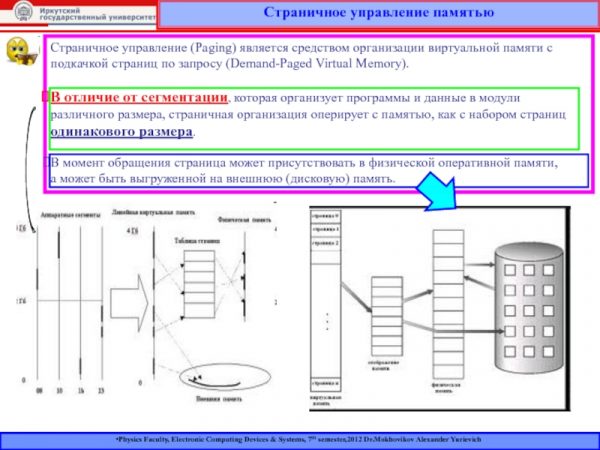

Чтобы избежать необходимости хранить большой объем информации для преобразования логических адресов в физические, адресное пространство делится на страницы одинакового размера (обычно 4 КиБ, но также 8 КиБ или больше), и для них сохраняются только данные сопоставления. Таким образом, виртуальное адресное пространство состоит из страниц, которые соответствуют областям одинакового размера в физической RAM.

Хотя логические страницы создают непрерывное линейное адресное пространство, размещение физических страниц является полностью случайным из-за преобразования. Это создает иллюзию для запущенного процесса, что его адресное пространство в ОЗУ непрерывно, хотя на самом деле физические страницы фрагментированы. Однако фрагментация скрыта от процесса (или его машинных инструкций), и ее не нужно решать каким-либо образом (в отличие от сегментации памяти, где фрагментацию необходимо устранять перемещением сегментов).

Перевод адресов

Трансляция адресов основана на идее разделения виртуального адресного пространства на страницы четко определенного размера. Размеры страниц могут различаться в зависимости от используемой архитектуры, но, с другой стороны, некоторые архитектуры поддерживают страницы разных размеров, часто параллельно. Однако обычно это порядка килобайт. Для 32 — битных Intel x86 процессоров , логический адрес 32-разрядное и размер страницы, как правило, 4кБ.

Пространство физической памяти разделено на непрерывные области того же размера, что и логические страницы. Эти области называются рамками страниц. Между логическими страницами и фреймом создается представление. Это представление обычно неполное, поскольку нормальный процесс не занимает все свое логическое пространство. Следовательно, существуют логические страницы без назначенного фрейма, так называемые недопустимые страницы. Могут быть кадры, которые не сопоставлены ни с одной логической страницей, или кадры, которым сопоставлены несколько логических страниц (например, общая память между процессами, будь то данные или общий код).

Таблица страниц

Таблица страниц — одна из реальных реализаций трансляции адресов. Предполагает линейное логическое адресное пространство. Логический адрес разделен на две части. Старшие биты считаются номером самой логической страницы (из-за линейной адресации порядка страниц в адресном пространстве), а младшие биты — смещением пространства памяти на данной странице. Для самого преобразования таблицы страниц используются только старшие биты, которые здесь служат индексом (обычно составным) в структуре таблиц подкачки.

Поиск в этой таблице приводит к номерам кадров и их флагам, которые важны, например, для защиты памяти от несанкционированного доступа. Полученный номер кадра физической страницы преобразуется в начальный адрес кадра в физической памяти путем сдвига битов влево. Наконец, смещение требуемого местоположения (младшие биты виртуального адреса) добавляется к базовому адресу (побитовое ИЛИ).

Таблица страниц может быть реализована непосредственно в оборудовании, но также может быть дополнительным алгоритмом, реализуемым операционной системой, если оборудование использует механизм, который не может поддерживать полное описание виртуального пространства.

Это сложное, но медленное решение из-за необходимости многократного доступа к ОЗУ.

TLB

TLB — это еще один подход к реализации разбиения на страницы, при котором несколько (порядка десятков) отображений логических страниц <-> физический фрейм хранятся в очень быстрой ассоциативной памяти непосредственно в процессоре MMU. Логический адрес, как и в таблицах подкачки, делится на верхнюю и нижнюю части, где более высокий — это индекс TLB, где ищется начальный адрес кадра, а меньший используется как смещение кадра. Некоторые архитектуры используют это решение разбиения на страницы в чистом виде, и если в TLB не будет найдено сопоставление, произойдет немедленный сбой.

Однако, поскольку трансляция происходит очень часто и если таблица страниц хранится в ОЗУ, что относительно медленно по сравнению со скоростью процессора , современные архитектуры ( x86 ) дополняют общие таблицы подкачки TLB в качестве значительного ускорения.